# SANYO Semiconductors

DATA SHEET

An ON Semiconductor Company

## BI-CMOS LSI PWM Current Control Stepping Motor Driver

### Overview

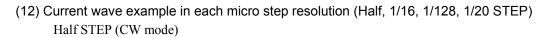

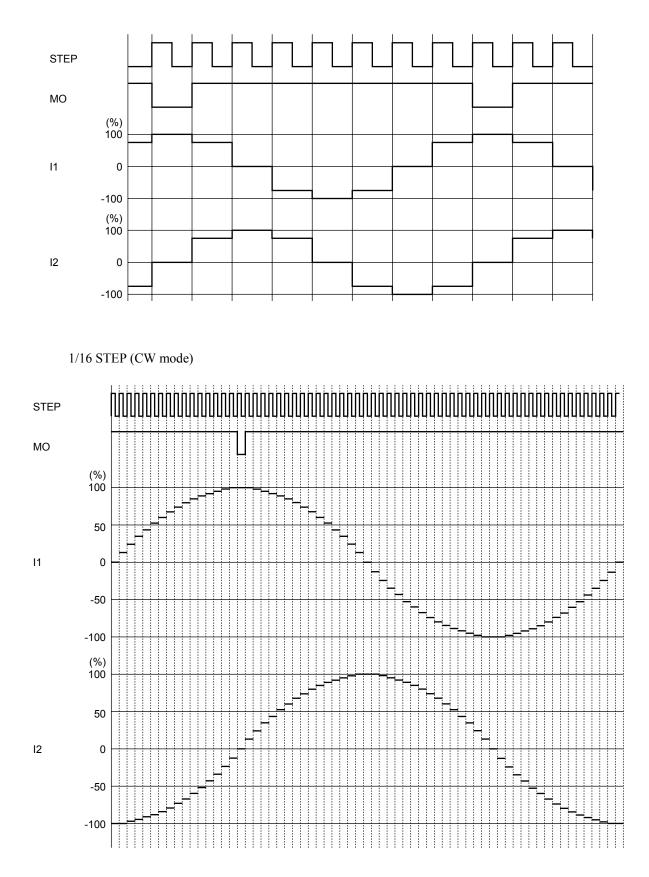

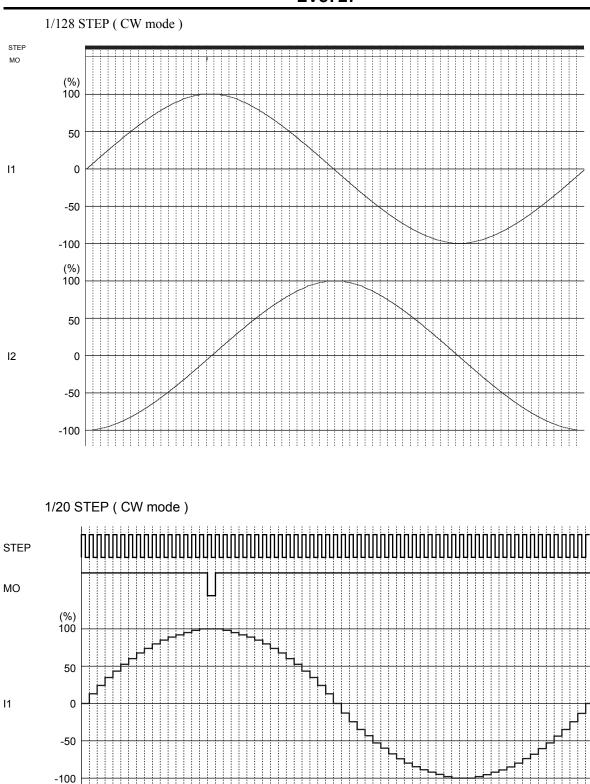

The LV8727 is a PWM current-controlled micro step bipolar stepping motor driver. This driver can do eight ways of micro step resolution of Half, 1/8, 1/16, 1/32, 1/64, 1/128, 1/10, 1/20 Step, and can drive simply by the step input.

#### Features

- Single-channel PWM current control stepping motor driver.

- Output on-resistance (upper side :  $0.25\Omega$ ; lower side :  $0.15\Omega$ ; total of upper and lower :  $0.4\Omega$ ; Ta = 25°C, IO = 4.0A)

- Half, 1/8, 1/16, 1/32, 1/64, 1/128, 1/10, 1/20 Step are selectable.

- Advance the excitation step with the only step signal input.

- BiCDMOS process IC.

- IO max=4.0A

- Input pull down resistance

- Available forward reverse control.

- Thermal shutdown circuit.

- With reset pin and enable pin.

## Specifications

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol                                 | Conditions        | Ratings     | Unit |

|-----------------------------|----------------------------------------|-------------------|-------------|------|

|                             | ,                                      | Conditions        | ő           |      |

| Supply voltage              | V <sub>M</sub> max                     |                   | 50          | V    |

| Output current              | I <sub>O</sub> max                     |                   | 4           | А    |

| Output peak current         | I <sub>O</sub> peak                    | tw≤10ms, duty 20% | 4.6         | А    |

| Logic input voltage         | V <sub>IN</sub> max                    |                   | 6           | V    |

| VREF input voltage          | VREF max                               |                   | 6           | V    |

| MO / DOWN pin input voltage | V <sub>MO</sub> /V <sub>DOWN</sub> max |                   | 6           | V    |

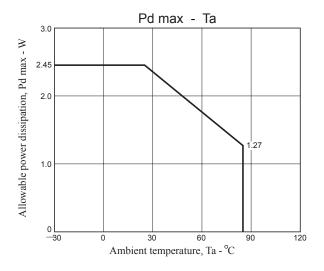

| Allowable power dissipation | Pd max                                 | Indipendent IC    | 2.45        | W    |

| Operating temperature       | Topr                                   |                   | -30 to +85  | °C   |

| Storage temperature         | Tstg                                   |                   | -55 to +150 | °C   |

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

■ Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment. The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for new introduction or other application different from current conditions on the usage of automotive device, communication device, office equipment, industrial equipment etc. , please consult with us about usage condition (temperature, operation time etc.) prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

## **Recommendation Operating Ratings** at $Ta = 25^{\circ}C$

| Parameter                | Symbol | Conditions | Ratings | Unit |

|--------------------------|--------|------------|---------|------|

| Supply voltage range     | VM     |            | 9 to 45 | V    |

| Logic input voltage      | VIN    |            | 0 to 5  | V    |

| VREF input voltage range | VREF   |            | 0 to 3  | V    |

## **Electrical Characteristics** at Ta = 25°C, $V_M$ = 24V, VREF = 1.5V

| Deservator                        | Oursels al           | Conditions                                     |       | Ratings |       |      |  |

|-----------------------------------|----------------------|------------------------------------------------|-------|---------|-------|------|--|

| Parameter                         | Symbol               | Conditions                                     | min   | typ     | max   | Unit |  |

| Standby mode current drain        | l <sub>M</sub> st    | ST = "L"                                       |       | 70      | 100   | μA   |  |

| Current drain                     | IM                   | ST = "H", OE = "H", no load                    |       | 3.5     | 4.9   | mA   |  |

| Thermal shutdown temperature      | TSD                  | Design guarantee                               | 150   | 180     | 200   | °C   |  |

| Thermal hysteresis width          | ∆TSD                 | Design guarantee                               |       | 40      |       | °C   |  |

| Logic pin input current           | IINL                 | V <sub>IN</sub> = 0.8V                         | 3     | 8       | 15    | μA   |  |

|                                   | IINH                 | V <sub>IN</sub> = 5V                           | 30    | 50      | 70    | μA   |  |

| Logic high-level input voltage    | V <sub>IN</sub> H    |                                                | 2.0   |         |       | V    |  |

| Logic low-level input voltage     | VINL                 |                                                |       |         | 0.8   | V    |  |

| FDT pin high-level voltage        | Vfdth                |                                                | 3.5   |         |       | V    |  |

| FDT pin middle-level voltage      | Vfdtm                |                                                | 1.1   |         | 3.1   | V    |  |

| FDT pin low-level voltage         | Vfdtl                |                                                |       |         | 0.8   | V    |  |

| Chopping frequency                | Fch                  | Cosc1 = 100pF                                  | 70    | 100     | 130   | kHz  |  |

| OSC1 pin charge/discharge current | losc1                |                                                | 7     | 10      | 13    | μA   |  |

| Chopping oscillation circuit      | Vtup1                |                                                | 0.8   | 1       | 1.2   | V    |  |

| threshold voltage                 | Vtdown1              |                                                | 0.3   | 0.5     | 0.7   | V    |  |

| VREF pin input voltage            | Iref                 | VREF = 1.5V                                    | -0.5  |         |       | μA   |  |

| DOWN output residual voltagr      | V <sub>O</sub> 1DOWN | Idown = 1mA                                    |       | 50      | 200   | mV   |  |

| MO pin residual voltage           | V <sub>O</sub> 1MO   | Imo = 1mA                                      |       | 50      | 200   | mV   |  |

| Hold current switching frequency  | Fdown                | Cosc2 = 1500pF                                 | 1.12  | 1.6     | 2.08  | Hz   |  |

| OSC2 pin charge/discharge current | losc2                |                                                | 7     | 10      | 13    | μA   |  |

| Hold current switching frequency  | Vtup2                |                                                | 0.8   | 1       | 1.2   | V    |  |

| threshold voltage                 | Vtdown2              |                                                | 0.3   | 0.5     | 0.7   | V    |  |

| Output on-resistance              | Ronu                 | I <sub>O</sub> = 4.0A, high-side ON resistance |       | 0.25    | 0.325 | Ω    |  |

|                                   | Rond                 | I <sub>O</sub> = 4.0A, low-side ON resistance  |       | 0.15    | 0.195 | Ω    |  |

| Output leakage current            | lOleak               | V <sub>M</sub> = 50V                           |       |         | 50    | μA   |  |

| Diode forward voltage             | VD                   | I <sub>D</sub> = -4.0A                         |       | 1       | 1.3   | V    |  |

| Current setting reference voltage | VRF                  | VREF = 1.5V, Current ratio 100%                | 0.485 | 0.5     | 0.515 | V    |  |

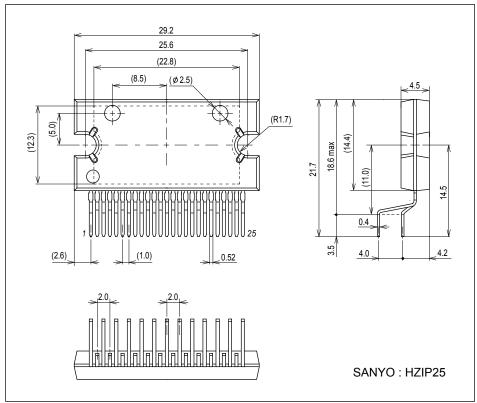

# Package Dimensions unit : mm (typ)

3236A

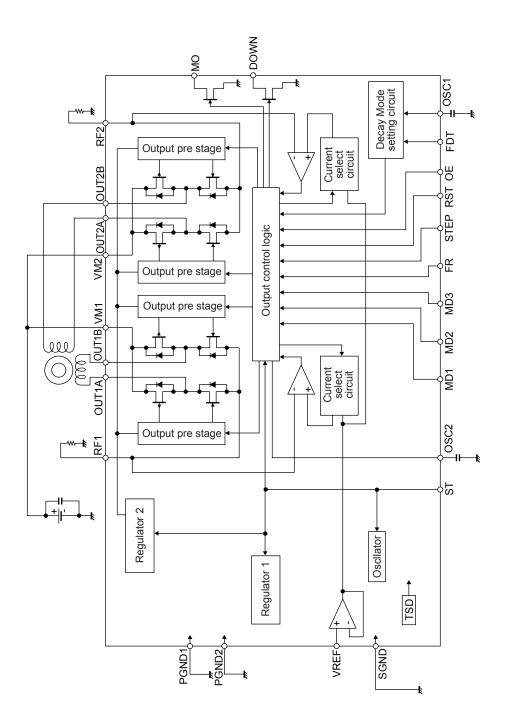

**Block Diagram**

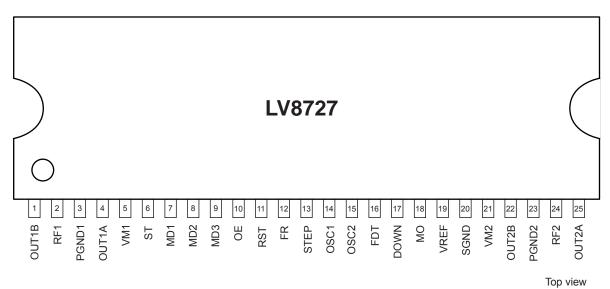

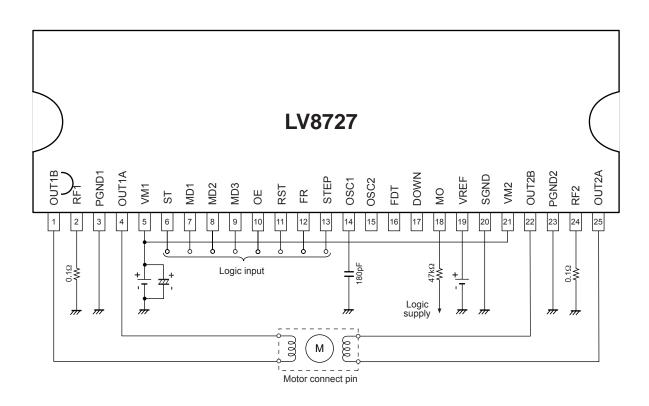

## Pin Assignment

#### **Pin Functions**

| Pin No. | Pin Name                             | Pin Functtion                                                            | Equivalent Circuit       |

|---------|--------------------------------------|--------------------------------------------------------------------------|--------------------------|

| 7       | MD1                                  | Excitation mode switching pin                                            |                          |

| 8       | MD2                                  | Excitation mode switching pin                                            | Internal 5V O            |

| 9       | MD3                                  | Excitation mode switching pin                                            |                          |

| 10      | OE                                   | Output enable signal input pin                                           |                          |

| 11      | RST                                  | Reset signal input pin                                                   | ╡ <u></u>                |

| 12      | FR                                   | Forward / Reverse signal input pin                                       | 10kΩ                     |

| 13      | STEP                                 | Clock pulse signal input pin                                             |                          |

|         |                                      |                                                                          |                          |

| 6       | ST                                   | Chip enable input pin.                                                   | Internal 5V<br>regulator |

|         |                                      |                                                                          |                          |

| 1       | OUT1B                                | Channel 1 OUTB output pin.                                               | (5)(21)                  |

| 2       | RF1                                  | Channel 1 current-sense resistor connection pin.                         |                          |

| 3       | PGND1                                | Channel 1 power GND                                                      |                          |

| 4       | OUT1A                                | Channel 1 OUTA output pin.                                               |                          |

| 5<br>21 | V <sub>M</sub> 1<br>V <sub>M</sub> 2 | Channel 1 motor supply connect pin<br>Channel 2 motor supply connect pin |                          |

| 21      | VM²<br>OUT2B                         | Channel 2 OUTB output pin.                                               |                          |

| 22      | PGND2                                | Channel 2 power GND                                                      |                          |

| 23      | RF2                                  | Channel 2 current-sense resistor connection pin.                         |                          |

| 25      | OUT2A                                | Channel 2 OUTA output pin.                                               | GND 0                    |

Continued on next page.

| Continued | from preceding | page.                                                                                                                       |                                                 |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Pin No.   | Pin Name       | Pin Functtion                                                                                                               | Equivalent Circuit                              |

| 19        | VREF           | Constant-current control reference voltage input pin.                                                                       | Internal 5V<br>regulator                        |

| 17        | DOWN           | Holding current output pin.                                                                                                 | Internal 5V                                     |

| 18        | MO             | Position detecting monitor pin.                                                                                             | Internal 5V<br>regulator                        |

| 14        | OSC1<br>OSC2   | Chopping frequency setting capacitor connection pin.<br>Holding current detection time setting capacitor<br>connection pin. | Internal 5V<br>regulator                        |

| 16        | FDT            | Decay mode select voltage input                                                                                             | Internal 5V<br>regulator<br>72kΩ<br>9kΩ<br>16kΩ |

#### **Reference describing operation**

#### (1) Stand-by function

When ST pin is at low levels, the IC enters stand-by mode, all logic is reset and output is turned OFF. When ST pin is at high levels, the stand-by mode is released.

#### (2) STEP pin function

STEP input advances electrical angle at every nising edge (advances step by step).

| Inj  | out     | Operating mode           |  |  |

|------|---------|--------------------------|--|--|

| ST   | STEP    |                          |  |  |

| Low  | *       | Standby mode             |  |  |

| High |         | Excitation step proceeds |  |  |

| High | <b></b> | Excitation step is kept  |  |  |

#### (3) Excitation setting method

Set the excitation setting as shown in the following table by setting MD1 pin, MD2 pin and MD3 pin.

|      | Input |      | Mode         | Initial position |             |  |

|------|-------|------|--------------|------------------|-------------|--|

| MD3  | MD2   | MD1  | (Excitation) | 1ch current      | 2ch current |  |

| Low  | Low   | Low  | Half         | 100%             | 0%          |  |

| Low  | Low   | High | 1/8          | 100%             | 0%          |  |

| Low  | High  | Low  | 1/16         | 100%             | 0%          |  |

| Low  | High  | High | 1/32         | 100%             | 0%          |  |

| High | Low   | Low  | 1/64         | 100%             | 0%          |  |

| High | Low   | High | 1/128        | 100%             | 0%          |  |

| High | High  | Low  | 1/10         | 100%             | 0%          |  |

| High | High  | High | 1/20         | 100%             | 0%          |  |

The initial position is also the default state at start-up and excitation position at counter-reset in each Micro step resolution.

#### (4) MO output pin

MO output pin serves as open-drain connection.

If MO pin will be in the state of an initial position, it is turned on, and it outputs a Low level.

| Excitation position    | МО   |

|------------------------|------|

| Initial position       | Low  |

| Other initial position | OPEN |

#### (5) Output current setting

Output current is set shown below by the VREF pin (applied voltage) and a resistance value between RF1(2) pin and GND.

$I_{OUT} = (VREF / 3) / RF1 (2)$  resistance

\* The setting value above is a 100% output current in each excitation mode.

(Example) When VREF = 0.9V and RF1 (2) resistance is  $0.1\Omega$ , the setting is shown below.

$I_{OUT} = (0.9V / 3) / 0.1\Omega = 3A$

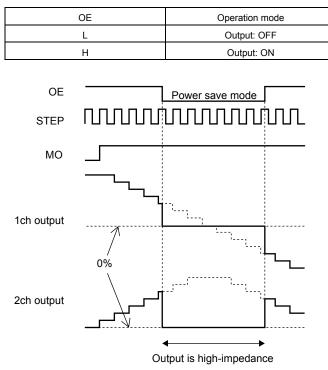

#### (6) Output enable function

When the OE pin is set Low, the output is forced OFF and goes to high impedance. However, the internal logic circuits are operating, so the excitation position proceeds when the STP is input. Therefore, when OE pin is returned to High, the output level conforms to the excitation position proceeded by the STEP input.

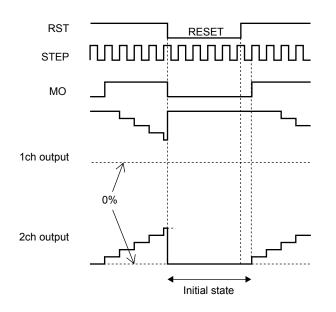

#### (7) Reset function

When the RST pin is set Low, the output goes to initial mode and excitation position is fixed in the initial position for STEP pin and FR pin input. MO pin outputs at low levels at the initial position. (Open drain connection)

| RST | Operation mode   |  |  |  |  |

|-----|------------------|--|--|--|--|

| Н   | Normal operation |  |  |  |  |

| L   | Reset state      |  |  |  |  |

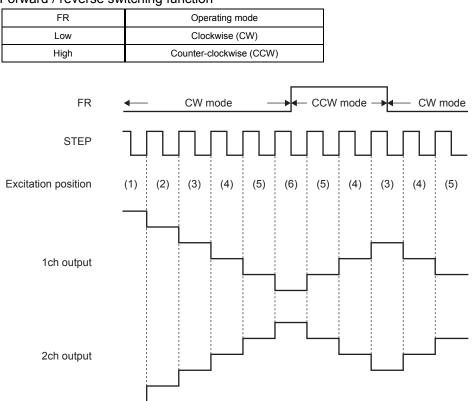

(8) Forward / reverse switching function

The internal D/A converter proceeds by a bit on the rising edge of the step signal input to the STEP pin. In addition, CW and CCW mode are switched by FR pin setting.

In CW mode, the channel 2 current phase is delayed by 90° relative to the channel 1 current.

In CCW mode, the channel 2 current phase is advanced by 90° relative to the channel 1 current.

#### (9) DECAY mode setting

Current DECAY method is selectable as shown below by applied voltage to the FDT pin.

| FDT voltage          | DECAY method |

|----------------------|--------------|

| 3.5V to              | SLOW DECAY   |

| 1.1V to 3.1V or OPEN | MIXED DECAY  |

| To 0.8V              | FAST DECAY   |

#### (10) Chopping frequency setting function

Chopping frequency is set as shown below by a capacitor between OSC1 pin and GND.  $Fcp = 1 / (Cosc1 / 10 \times 10^{-6}) (Hz)$

(Example) When Cosc1 = 180pF, the chopping frequency is shown below. Fcp =  $1 / (180 \times 10^{-12} / 10 \times 10^{-6}) = 55.6$ (kHz)

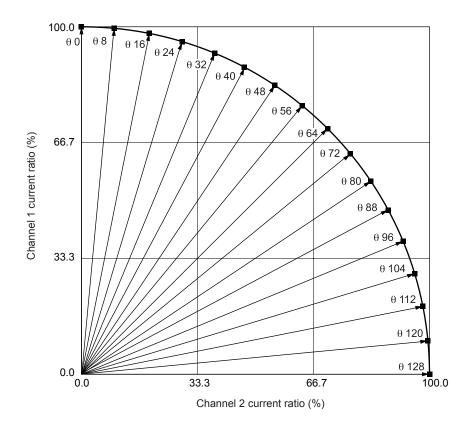

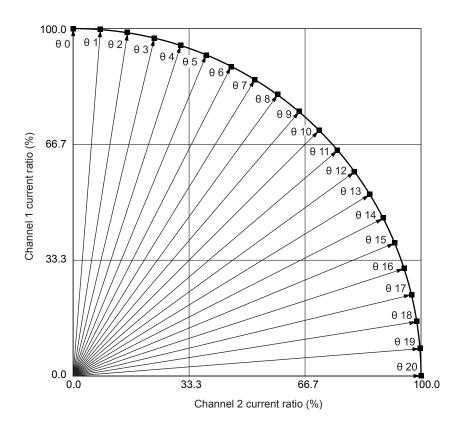

#### (11) Output current in each micro step resolution

Output current vector locus (one step is normalized to 90 degrees) Half, 1/8, 1/16, 1/32, 1/64, 1/128 Step

#### Current setting ratio in each micro step resolution

| STEP | 1/128 | 8 (%) | 1/64 | (%) | 1/32 | (%) | 1/1  | 6 (%) | 1/8 | (%) | Half | ·(%) |

|------|-------|-------|------|-----|------|-----|------|-------|-----|-----|------|------|

| STEP | 1ch   | 2ch   | 1ch  | 2ch | 1ch  | 2ch | 1 ch | 2ch   | 1ch | 2ch | 1ch  | 2ch  |

| θ0   | 100   | 0     | 100  | 0   | 100  | 0   | 100  | 0     | 100 | 0   | 100  | 0    |

| θ1   | 100   | 1     |      |     |      |     |      |       |     |     |      |      |

| θ2   | 100   | 2     | 100  | 2   |      |     |      |       |     |     |      |      |

| θ3   | 100   | 4     |      |     |      |     |      |       |     |     |      |      |

| θ4   | 100   | 5     | 100  | 5   | 100  | 5   |      |       |     |     |      |      |

| θ5   | 100   | 6     |      |     |      |     |      |       |     |     |      |      |

| θ6   | 100   | 7     | 100  | 7   |      |     |      |       |     |     |      |      |

| θ7   | 100   | 9     |      |     |      |     |      |       |     |     |      |      |

| θ8   | 100   | 10    | 100  | 10  | 100  | 10  | 100  | 10    |     |     |      |      |

| θ9   | 99    | 11    |      |     |      |     |      |       |     |     |      |      |

| θ10  | 99    | 12    | 99   | 12  |      |     |      |       |     |     |      |      |

| θ11  | 99    | 13    |      |     |      |     |      |       |     |     |      |      |

| θ12  | 99    | 15    | 99   | 15  | 99   | 15  |      |       |     |     |      |      |

| θ13  | 99    | 16    |      |     |      |     |      |       |     |     |      |      |

| θ14  | 99    | 17    | 99   | 17  |      |     |      |       |     |     |      |      |

| θ15  | 98    | 18    |      |     |      |     |      |       |     |     |      |      |

| θ16  | 98    | 20    | 98   | 20  | 98   | 20  | 98   | 20    | 98  | 20  |      |      |

| θ17  | 98    | 21    |      |     |      |     |      |       |     |     |      |      |

| θ18  | 98    | 22    | 98   | 22  |      |     |      |       |     |     |      |      |

| θ19  | 97    | 23    |      |     |      |     |      |       |     |     |      |      |

| θ20  | 97    | 24    | 97   | 24  | 97   | 24  |      |       |     |     |      |      |

| θ21  | 97    | 25    |      |     |      |     |      |       |     |     |      |      |

| θ22  | 96    | 27    | 96   | 27  |      |     |      |       |     |     |      |      |

| θ23  | 96    | 28    |      |     |      |     |      |       |     |     |      |      |

| θ24  | 96    | 29    | 96   | 29  | 96   | 29  | 96   | 29    |     |     |      |      |

| θ25  | 95    | 30    |      |     |      |     |      |       |     |     |      |      |

Continued on next page.

| OTER                                          | 1/128                | 8 (%)    | 1/64     | · (%)      | 1/32 | . (%) | 1/16 (%) |     | 1/8 | (%)      | Halfe (%)    |          |

|-----------------------------------------------|----------------------|----------|----------|------------|------|-------|----------|-----|-----|----------|--------------|----------|

| STEP                                          | 1ch                  | 2ch      | 1 ch     | 2ch        | 1ch  | 2ch   | 1ch      | 2ch | 1ch | 2ch      | 1ch          | 2ch      |

| θ26                                           | 95                   | 31       | 95       | 31         |      |       |          |     |     |          |              |          |

| θ27                                           | 95                   | 33       |          |            |      |       |          |     |     |          |              |          |

| θ28                                           | 94                   | 34       | 94       | 34         | 94   | 34    |          |     |     |          |              |          |

| θ29                                           | 94                   | 35       | 74       | 54         | 74   | 54    |          |     |     |          |              |          |

| θ30                                           | 93                   | 36       | 93       | 36         |      |       |          |     |     |          |              |          |

| θ31                                           | 93                   | 37       | ,5       | 50         |      |       |          |     |     |          |              |          |

|                                               |                      |          | 02       | 20         | 02   | 20    | 02       | 20  | 02  | 20       |              |          |

| θ32<br>022                                    | 92                   | 38       | 92       | 38         | 92   | 38    | 92       | 38  | 92  | 38       |              |          |

| θ33                                           | 92                   | 39       |          |            |      |       |          |     |     |          |              |          |

| θ34                                           | 91                   | 41       | 91       | 41         |      |       |          |     |     |          |              |          |

| θ35                                           | 91                   | 42       |          |            |      |       |          |     |     |          |              |          |

| θ36                                           | 90                   | 43       | 90       | 43         | 90   | 43    |          |     |     |          |              |          |

| θ37                                           | 90                   | 44       |          |            |      |       | -        |     |     |          |              |          |

| θ38                                           | 89                   | 45       | 89       | 45         |      |       |          |     |     |          |              |          |

| θ39                                           | 89                   | 46       |          |            |      |       |          |     |     |          | <u> </u>     |          |

| θ40                                           | 88                   | 47       | 88       | 47         | 88   | 47    | 88       | 47  |     |          |              |          |

| θ41                                           | 88                   | 48       |          |            |      |       |          |     |     |          |              |          |

| θ42                                           | 87                   | 49       | 87       | 49         |      |       |          |     |     |          |              |          |

| θ43                                           | 86                   | 50       |          |            |      |       |          |     |     |          |              |          |

| θ44                                           | 86                   | 51       | 86       | 51         | 86   | 51    |          |     |     |          |              |          |

| θ45                                           | 85                   | 52       |          |            |      |       |          |     |     |          |              |          |

| θ46                                           | 84                   | 53       | 84       | 53         | Γ    |       |          |     | Γ   | Ι        | [            |          |

| θ47                                           | 84                   | 55       |          |            |      |       |          |     |     |          |              |          |

| θ48                                           | 83                   | 56       | 83       | 56         | 83   | 56    | 83       | 56  | 83  | 56       |              |          |

| θ49                                           | 82                   | 57       |          |            |      |       |          |     |     |          |              |          |

| θ50                                           | 82                   | 58       | 82       | 58         |      |       |          |     |     |          |              |          |

| θ51                                           | 81                   | 59       | 82       | 50         |      |       |          |     |     |          |              |          |

| θ52                                           | 80                   | 60       | 80       | 60         | 80   | 60    |          |     |     |          |              |          |

|                                               |                      |          | 80       | 60         | 80   | 60    | -        |     |     |          |              |          |

| θ53                                           | 80                   | 61       | 70       | (2)        |      |       |          |     |     |          |              |          |

| θ54                                           | 79                   | 62       | 79       | 62         |      |       |          |     |     |          |              |          |

| θ55                                           | 78                   | 62       |          |            |      |       | -        |     |     |          |              |          |

| θ56                                           | 77                   | 63       | 77       | 63         | 77   | 63    | 77       | 63  |     |          |              |          |

| θ57                                           | 77                   | 64       |          |            |      |       |          |     |     |          | <u> </u>     |          |

| θ58                                           | 76                   | 65       | 76       | 65         |      |       |          |     |     |          |              |          |

| θ59                                           | 75                   | 66       |          |            |      |       |          |     |     |          |              |          |

| θ60                                           | 74                   | 67       | 74       | 67         | 74   | 67    |          |     |     |          |              |          |

| θ61                                           | 73                   | 68       |          |            |      |       |          |     |     |          |              |          |

| θ62                                           | 72                   | 69       | 72       | 69         |      |       |          |     |     |          |              |          |

| θ63                                           | 72                   | 70       |          |            |      |       |          |     |     |          |              |          |

| θ64                                           | 71                   | 71       | 71       | 71         | 71   | 71    | 71       | 71  | 71  | 71       | 71           | 71       |

| θ65                                           | 70                   | 72       |          |            |      |       |          |     |     |          |              |          |

| θ66                                           | 69                   | 72       | 69       | 72         |      |       |          |     |     |          |              |          |

| θ67                                           | 68                   | 73       |          |            |      |       |          |     |     |          |              |          |

| θ68                                           | 67                   | 74       | 67       | 74         | 67   | 74    |          |     | 1   |          | 1            |          |

| θ69                                           | 66                   | 75       | <i>,</i> | <i>.</i> . |      |       |          |     |     |          | <u> </u>     | 1        |

| θ70                                           | 65                   | 76       | 65       | 76         |      |       |          |     |     |          | <u> </u>     |          |

| θ70<br>θ71                                    | 64                   | 70       | 05       | 70         |      |       |          |     |     | <u> </u> | <u> </u>     | 1        |

|                                               | 63                   |          | 62       | 77         | 62   | 77    | 62       | 77  |     |          | <u> </u>     |          |

| θ72<br>072                                    |                      | 77       | 63       | 77         | 63   | 77    | 63       | 77  |     |          | <del> </del> |          |

| θ73                                           | 62                   | 78       | (2)      | 70         |      |       |          |     |     |          | <u> </u>     | <u> </u> |

| θ74                                           | 62                   | 79       | 62       | 79         |      |       |          |     |     |          | <u> </u>     |          |

| θ75                                           | 61                   | 80       |          |            |      |       |          |     |     |          | <u> </u>     | <u> </u> |

| θ76                                           | 60                   | 80       | 60       | 80         | 60   | 80    |          |     |     |          | ───          |          |

| θ77                                           | 59                   | 81       |          | ļ          |      | ļ     |          |     |     | ļ        | ───          |          |

| θ78                                           | 58                   | 82       | 58       | 82         |      |       |          |     |     | L        | <u> </u>     |          |

| θ79                                           | 57                   | 82       |          |            |      |       |          |     |     |          | <u> </u>     |          |

| θ80                                           | 56                   | 83       | 56       | 83         | 56   | 83    | 56       | 83  | 56  | 83       |              |          |

| 0.01                                          | 55                   | 84       |          |            |      |       |          |     |     |          |              |          |

| θ81                                           | 53                   | 84       | 53       | 84         |      |       |          |     |     |          |              |          |

| θ81<br>θ82                                    | 52                   | 85       |          |            |      |       |          |     |     |          |              |          |

|                                               |                      | 86       | 51       | 86         | 51   | 86    |          |     |     |          | l            | 1        |

| θ82<br>θ83                                    |                      |          |          |            |      |       |          |     | l   | 1        | 1            |          |

| <ul><li>θ82</li><li>θ83</li><li>θ84</li></ul> | 51                   | 86       |          |            |      |       |          |     |     | 1        | +            | +        |

| θ82   θ83   θ84   θ85                         | 51<br>50             | 86<br>87 | 49       | 87         |      |       |          |     |     |          |              |          |

| θ82   θ83   θ84   θ85   θ86                   | 51<br>50<br>49       | 87       | 49       | 87         |      |       |          |     |     |          |              |          |

| θ82   θ83   θ84   θ85   θ86   θ87             | 51<br>50<br>49<br>48 | 87<br>88 |          |            | 47   | 00    | 17       | 00  |     |          |              |          |

| θ82   θ83   θ84   θ85   θ86                   | 51<br>50<br>49       | 87       | 49<br>47 | 87<br>88   | 47   | 88    | 47       | 88  |     |          |              |          |

Continued on next page.

| STEP | 1/128 (%) |     | 1/64 (%) |     | 1/32 (%) |     | 1/16 (%) |     | 1/8 (%) |     | Half (%) |     |

|------|-----------|-----|----------|-----|----------|-----|----------|-----|---------|-----|----------|-----|

|      | 1ch       | 2ch | 1ch      | 2ch | 1ch      | 2ch | 1ch      | 2ch | 1ch     | 2ch | 1ch      | 2ch |

| θ91  | 44        | 90  |          |     |          |     |          |     |         |     |          |     |

| θ92  | 43        | 90  | 43       | 90  | 43       | 90  |          |     |         |     |          |     |

| θ93  | 42        | 91  |          |     |          |     |          |     |         |     |          |     |

| θ94  | 41        | 91  | 41       | 91  |          |     |          |     |         |     |          |     |

| θ95  | 39        | 92  |          |     |          |     |          |     |         |     |          |     |

| θ96  | 38        | 92  | 38       | 92  | 38       | 92  | 38       | 92  | 38      | 92  |          |     |

| θ97  | 37        | 93  |          |     |          |     |          |     |         |     |          |     |

| θ98  | 36        | 93  | 36       | 93  |          |     |          |     |         |     |          |     |

| θ99  | 35        | 94  |          |     |          |     |          |     |         |     |          |     |

| θ100 | 34        | 94  | 34       | 94  | 34       | 94  |          |     |         |     |          |     |

| θ101 | 33        | 95  |          |     |          |     |          |     |         |     |          |     |

| θ102 | 31        | 95  | 31       | 95  |          |     |          |     |         |     |          |     |

| θ103 | 30        | 95  |          |     |          |     |          |     |         |     |          |     |

| θ104 | 29        | 96  | 29       | 96  | 29       | 96  | 29       | 96  |         |     |          |     |

| θ105 | 28        | 96  |          |     |          |     |          |     |         |     |          |     |

| θ106 | 27        | 96  | 27       | 96  |          |     |          |     |         |     |          |     |

| θ107 | 25        | 97  |          |     |          |     |          |     |         |     |          |     |

| θ108 | 24        | 97  | 24       | 97  | 24       | 97  |          |     |         |     |          |     |

| θ109 | 23        | 97  |          |     |          |     |          |     |         |     |          |     |

| θ110 | 22        | 98  | 22       | 98  |          |     |          |     |         |     |          |     |

| θ111 | 21        | 98  |          |     |          |     |          |     |         |     |          |     |

| θ112 | 20        | 98  | 20       | 98  | 20       | 98  | 20       | 98  | 20      | 98  |          |     |

| θ113 | 18        | 98  |          |     |          |     |          |     |         |     |          |     |

| θ114 | 17        | 99  | 17       | 99  |          |     |          |     |         |     |          |     |

| θ115 | 16        | 99  |          |     |          |     |          |     |         |     |          |     |

| θ116 | 15        | 99  | 15       | 99  | 15       | 99  |          |     |         |     |          |     |

| θ117 | 13        | 99  |          |     |          |     |          |     |         |     |          |     |

| θ118 | 12        | 99  | 12       | 99  |          |     |          |     |         |     |          |     |

| θ119 | 11        | 99  |          |     |          |     |          |     |         |     |          |     |

| θ120 | 10        | 100 | 10       | 100 | 10       | 100 | 10       | 100 |         |     |          |     |

| θ121 | 9         | 100 |          |     |          |     |          |     |         |     |          |     |

| θ122 | 7         | 100 | 7        | 100 |          |     |          |     |         |     |          |     |

| θ123 | 6         | 100 |          |     |          |     |          |     |         |     |          |     |

| θ124 | 5         | 100 | 5        | 100 | 5        | 100 |          |     |         |     |          |     |

| θ125 | 4         | 100 |          |     |          |     |          |     |         |     |          |     |

| θ126 | 2         | 100 | 2        | 100 |          |     |          |     |         |     |          |     |

| θ127 | 1         | 100 |          |     |          |     |          |     |         |     |          |     |

| θ128 | 0         | 100 | 0        | 100 | 0        | 100 | 0        | 100 | 0       | 100 | 0        | 100 |

Output current vector locus (one step is normalized to 90 degrees) 1/10, 1/20 STEP

Current setting ratio in each micro step resolution 1/10, 1/20 STEP

| STEP | 1/20 | (%) | 1/10 (%) |     |  |

|------|------|-----|----------|-----|--|

| SIEP | 1ch  | 2ch | 1 ch     | 2ch |  |

| θ0   | 100  | 0   | 100      | 0   |  |

| θ1   | 100  | 8   |          |     |  |

| θ2   | 99   | 16  | 99       | 16  |  |

| θ3   | 97   | 23  |          |     |  |

| θ4   | 95   | 31  | 95       | 31  |  |

| θ5   | 92   | 38  |          |     |  |

| θ6   | 89   | 45  | 89       | 45  |  |

| θ7   | 85   | 52  |          |     |  |

| θ8   | 81   | 59  | 81       | 59  |  |

| θ9   | 76   | 65  |          |     |  |

| θ10  | 71   | 71  | 71       | 71  |  |

| θ11  | 65   | 76  |          |     |  |

| θ12  | 59   | 81  | 59       | 81  |  |

| θ13  | 52   | 85  |          |     |  |

| θ14  | 45   | 89  | 45       | 89  |  |

| θ15  | 38   | 92  |          |     |  |

| θ16  | 31   | 95  | 31       | 95  |  |

| θ17  | 23   | 97  |          |     |  |

| θ18  | 16   | 99  | 16       | 99  |  |

| θ19  | 8    | 100 |          |     |  |

| θ20  | 0    | 100 | 0        | 100 |  |

(%) 100

50

0

-50

-100

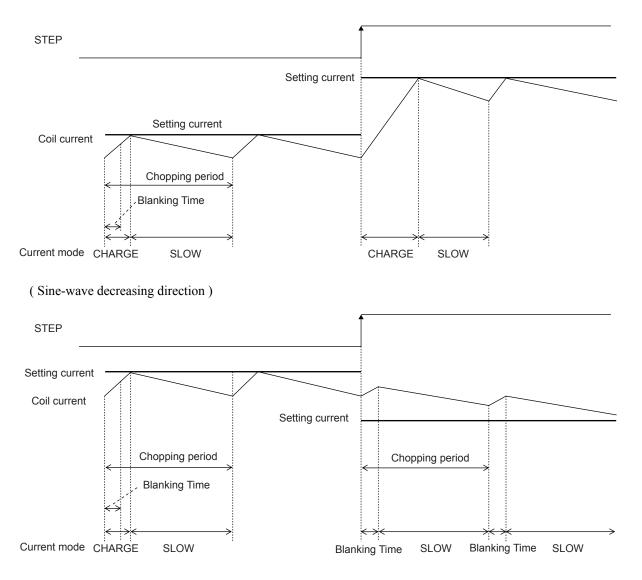

#### (13) Current control operation

SLOW DECAY current control operation

When FDT pin voltage is a voltage over 3.5V, the constant-current control is operated in SLOW DECAY mode. (Sine-wave increasing direction)

Each of current modes operates with the follow sequence.

The IC enters CHARGE mode at a rising edge of the chopping oscillation. ( A period of CHARGE mode (Blanking Time) is forcibly present in approximately  $1\mu$ s, regardless of the current value of the coil current (ICOIL) and set current (IREF)).

After the period of the blanking time, the IC operates in CHARGE mode until ICOIL  $\geq$  IREF. After that, the mode switches to the SLOW DECAY mode and the coil current is attenuated until the end of a chopping period. At the constand-current in SLOW DECAY mode, following to the setting current from the coil current may take time (or not follow) for the current delay attenuation.

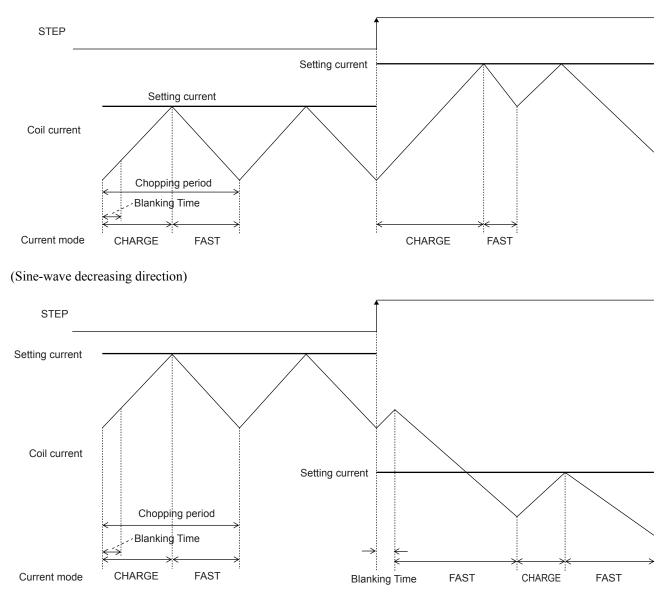

#### FAST DECAY current control operation

When FDT pin voltage is a voltage under 0.8V, the constant-current control is operated in FAST DECAY mode. (Sine-wave inxreasing direction)

Each of current modes operates with the follow sequence.

The IC enters CHARGE mode at a rising edge of the chopping oscillation. ( A period of CHARGE mode (Blanking Time) is forcibly present in approximately 1µs, regardless of the current value of the coil current (ICOIL) and set current (IREF)).

After the period of the blanking time, the IC operates in CHARGE mode until ICOIL  $\geq$  IREF. After that, the mode switches to the FAST DECAY mode and the coil current is attenuated until the end of a chopping period. At the constand-current control in FAST DECAY mode, following to the setting current from the coil current take short-time for the current fast attenuation, but, the current ripple value may be higher.

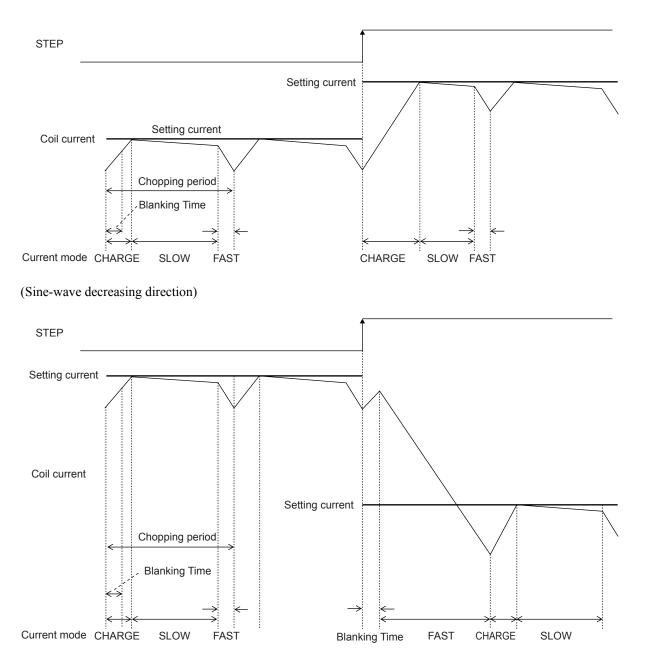

#### MIXED DECAY current control operation

When FDT pin voltage is a voltage between 1.1V to 3.1V or OPEN, the constant-current control is operated in MIXED DECAY mode.

(Sine-wave increasing direction)

Each of current modes operates with the follow sequence.

The IC enters CHARGE mode at a rising edge of the chopping oscillation. ( A period of CHARGE mode (Blanking Time) is forcibly present in approximately 1µs, regardless of the current value of the coil current (ICOIL) and set current (IREF)).

In a period of Blanking Time, the coil current (ICOIL) and the setting current (IREF) are compared.

If an ICOIL < IREF state exists during the charge period:

The IC operates in CHARGE mode until ICOIL  $\geq$  IREF. After that, it switches to SLOW DECAY mode and then switches to FAST DECAY mode in the last approximately 1µs of the period.

If no ICOIL < IREF state exists during the charge period:

The IC switches to FAST DECAY mode and the coil current is attenuated with the FAST DECAY operation until the end of a chopping period.

The above operation is repeated. Normally, in the sine wave increasing direction the IC operates in SLOW (+ FAST) DECAY mode, and in the sine wave decreasing direction the IC operates in FAST DECAY mode until the current is attenuated and reaches the set value and the IC operates in SLOW (+ FAST) DECAY mode.

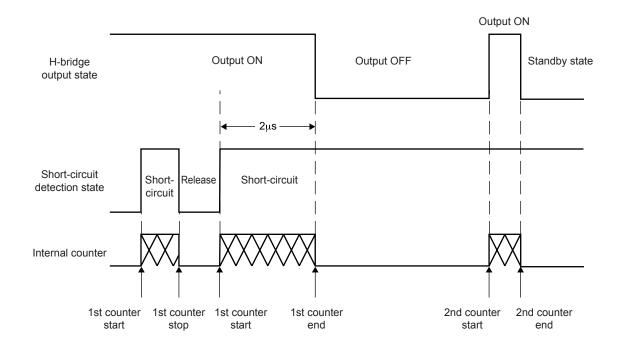

#### (13) Output short-circuit protection circuit

Built-in output short-circuit protection circuit makes output to enter in stand-by mode. This function prevents the IC from damaging when the output shorts circuit by a voltage short or a ground short, etc. When output short state is detected, short-circuit detection circuit state the operating and output is once turned OFF. Subsequently, the output is turned ON again after the timer latch period (typ.  $256\mu$ s). If the output remains in the short-circuit state, turn OFF the output, fix the output to the wait mode, and turn ON the EMO output.

When output is fixed in stand-by mode by output short protection circuit, output is released the latch by setting ST ="L".

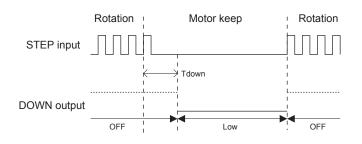

#### (15) DOWN output pin

The DOWN output pin is an open-drain connection.

This pin is turned ON when no rising edge of STEP between the input signals while a period determined by a capacitor between OSC2 and GND, and outputs at low levels.

The open-drain output in once turned ON, is turned OFF at the next rising edge of STEP.

Holding current switching time (Tdown) is set as shown below by a capacitor between OSC2 pin and GND. Tdown =  $Cosc2 \times 0.4 \times 10^9$  (s)

(Example) When Cosc2 = 1500 pF, the STEM signal detection time is shown below.

Tdown = 1500pF x 0.4 x 109 = 0.6 (s)

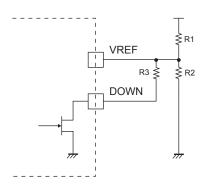

By connecting circumference parts like the example of the following circuit diagram using a DOWN pin, that is a STEP signal is not inputted more than detection time, it is a DOWN output's turning on in the state of holding turning on electricity the position of a stepping motor, and setting current's falling because VREF input voltage's falls, and stopping power consumption -- it can do.

(Example) When V1=5V, R1=27k $\Omega$ , R2=4.7k $\Omega$ , R3=1k $\Omega$ , the VREF input voltage is shown below. DOWN output OFF: VREF=V1×R2/(R1+R2)=0.741V DOWN output ON: VREF=V1×(R2 || R3)/ (R1+(R2 || R3))=0.126V

## **Application Circuit Example**

The above sample application circuit is set to the following conditions:

```

\label{eq:constant-current setting} $$ IOUT=VREF/3/RF$$ (Example) When is VREF=0.9V$$ IOUT=0.9V/3/0.1\Omega=3A$ $$ Chopping frequency setting $$ Fchop=Ichop/(Cchop×Vt×2)$$ =10\muA/(180pF×0.5V×2)=55.6kHz$ $$

```

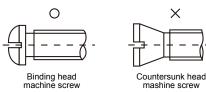

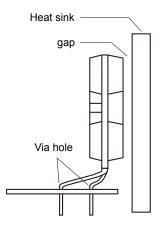

#### HZIP25 Heat sink attachment

Heat sinks are used to lower the semiconductor device junction temperature by leading the head generated by the device to the outer environment and dissipating that heat.

- a. Unless otherwise specified, for power ICs with tabs and power ICs with attached heat sinks, solder must not be applied to the heat sink or tabs.

- b. Heat sink attachment

- $\cdot$  Use flat-head screws to attach heat sinks.

- $\cdot$  Use also washer to protect the package.

- · Use tightening torques in the ranges 39-59Ncm(4-6kgcm).

- If tapping screws are used, do not use screws with a diameter larger than the holes in the semiconductor device itself.

- Do not make gap, dust, or other contaminants to get between the semiconductor device and the tab or heat sink.

- Take care a position of via hole.

- $\cdot$  Do not allow dirt, dust, or other contaminants to get between the semiconductor device and the tab or heat sink.

- · Verify that there are no press burrs or screw-hole burrs on the heat sink.

- · Warping in heat sinks and printed circuit boards must be no more than

- 0.05 mm between screw holes, for either concave or convex warping.

- · Twisting must be limited to under 0.05 mm.

- $\cdot$  Heat sink and semiconductor device are mounted in parallel.

- Take care of electric or compressed air drivers

- The speed of these torque wrenches should never exceed 700 rpm, and should typically be about 400 rpm.

- c. Silicone grease

- $\cdot$  Spread the silicone grease evenly when mounting heat sinks.

- · Sanyo recommends YG-6260 (Momentive Performance Materials Japan LLC)

- d. Mount

- · First mount the heat sink on the semiconductor device, and then mount that assembly on the printed circuit board.

- $\cdot$  When attaching a heat sink after mounting a semiconductor device into the printed circuit board, when tightening up a heat sink with the screw, the mechanical stress which is impossible to the semiconductor device and the pin doesn't hang.

- e. When mounting the semiconductor device to the heat sink using jigs, etc.,

- $\cdot$  Take care not to allow the device to ride onto the jig or positioning dowel.

- $\cdot$  Design the jig so that no unreasonable mechanical stress is not applied to the semiconductor device.

- f. Heat sink screw holes

- · Be sure that chamfering and shear drop of heat sinks must not be larger than the diameter of screw head used.

- $\cdot$  When using nuts, do not make the heat sink hole diameters larger than the diameter of the head of the screws used. A hole diameter about 15% larger than the diameter of the screw is desirable.

- $\cdot$  When tap screws are used, be sure that the diameter of the holes in the heat sink are not too small. A diameter about 15% smaller than the diameter of the screw is desirable.

- g. There is a method to mount the semiconductor device to the heat sink by using a spring band. But this method is not recommended because of possible displacement due to fluctuation of the spring force with time or vibration.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of November, 2011. Specifications and information herein are subject to change without notice.